# Full-power converter based test bench for low voltage ride-through testing of wind turbine converters

Topic 14c: Converters for rotating and linear generators, Fault ride through methods, Origin: Industry (I)

Abstract—This paper describes a full converter based test bench to generate faulted grid voltages for fault ride-through (FRT) testing of the full-power converter based wind turbine drive. Principles of the test bench control and the generation of different types of voltage dips are explained. Measurement results of a down-scaled 8.3 kVA laboratory test bench are shown. The target system, a MW-scale test bench will be commissioned until the end of year 2010.

# I. INTRODUCTION

With an increasing share of electricity produced by wind power, the behaviour of wind turbines during grid faults has become of great importance. More and more often grid code specifications require that wind turbines must be able to ride through all kinds of grid faults, including faults with very low remaining voltage levels and unsymmetrical (1-phase and 2-phase) faults [1]. From the control engineering point of view, continuously tougher grid code requirements present many control challenges for wind turbine converter control. Although the on-site tests are necessary to prove the fault ridethrough (FRT) compliance of wind turbines, in developing stage of the converter control, it is a common procedure to simulate, test and analyse the system performance in a laboratory test bench. For this purpose, a grid emulator capable of generating defined, repeatable voltage dips of variable magnitude, duration and fault type, is needed.

According to [2] there are generally four different types of voltage dip generators: 1) rotating generator based, 2) shunt (or switched) impedance based, 3) transformer based and 4) full converter based. Shunt impedance based solutions are most often used and they are also recognized as a standardized way to create voltage dips [3],[4]. Because the shunt impedance solutions are typically used to generate voltage dips in the medium voltage level, medium voltage switchgears and adjustable inductors are needed. Moreover, if this solution is about to be used at the production facilities, an independent medium voltage feeder with sufficient high short-circuit ratio and dedicated only for testing purposes is typically required in order to get the permission from the local distribution network operator and to limit the influences of the voltage dip on the supplying grid.

Transformer based voltage dip generators, although claimed to be low cost solutions and simple to control [2], requires bulky variable output transformer and practically a same number of power electronic switches (four per phase), such as IGBT with anti-parallel diode, as the full converter based solution. In order to prevent an overvoltage at the transformer output and to protect the IGBTs from overvoltage when switching off large inductive currents slow switching of the IGBTs and snubber circuits have to be used.

Full converter based test benches consist of back-toback converter connected between the grid and the equipment under test (EUT). By controlling the EUT-side output voltage several types of grid faults can be emulated. Examples of such devices in down-scaled size are described in [5] and in MW-scale in [6]. A comparison between a transformer based and a full converter based voltage dip generator can be found in [7]. It is concluded that the full converter setup has small size, light weight, and is more powerful compared with transformer based solution, but due to the claimed disadvantages of the complex control, high cost and lower reliability due to the limited overvoltage and overcurrent capabilities of the IGBTs the transformer based sag generator is the preferred solution for laboratory type application.

For full power converter manufacturer, however, the full converter based test bench is the preferable choice, because exactly the same converter hardware, filter components and control software can be used to build the test bench. Straightforward open loop type scalar control with simple dip generation functions is found to be sufficient for the grid emulator voltage control.

## II. FULL-POWER CONVERTER BASED TEST BENCH

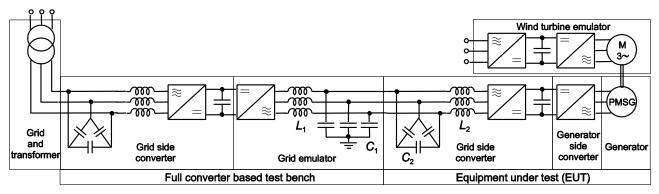

Topology of full-power converter based test bench is shown in Fig. 1. The EUT, which is a full-power back-toback converter connected permanent magnet synchronous generator (PSMG), is supplied by an identical full-power back-to-back converter. The grid side converter of the test bench controls the DC-link voltage to its reference and serves as a power supply to the grid emulator. Grid emulator converter operates as a controllable AC voltage source and generates voltage dips and frequency by using an inbuilt function generator. Both symmetrical and unsymmetrical voltage faults can be emulated. To ensure a good quality of the emulator output voltage, which is produced by means of space-vector pulse width modulation (SVPWM), an LC-filter is used. Part of the filter capacitance is introduced by the LC-filter of the EUT, but because these capacitors can be deltaconnected, a separate star-connected capacitor branch is introduced. Star point is grounded to prevent the common mode voltage from distorting the phase-to-ground voltages of the grid emulator. Main parameters of the down-scaled and the target full-scale test benches are shown in Table I.

#### III. TEST BENCH CONTROL AND VOLTAGE DIP GENERATION

Symmetrical three-phase output voltage with given frequency  $\omega_{ref} = 2\pi f_{ref}$  is produced by giving the voltage space-vector reference to SVPWM as

Fig. 1: Overview of the full converter based LVRT test bench.

$$\underline{u}_{\rm ref}(t) = \sqrt{\frac{2}{3}} U_{\rm ref} e^{j\omega_{\rm ref}t} = \sqrt{\frac{2}{3}} U_{\rm ref} \left(\cos(\omega_{\rm ref}t) + j\sin(\omega_{\rm ref}t)\right)$$

(1)

$$= u_{\rm x,ref}(t) + ju_{\rm y,ref}(t)$$

where  $U_{\rm ref}$  is the reference of the grid emulator phase-tophase output voltage in rms.

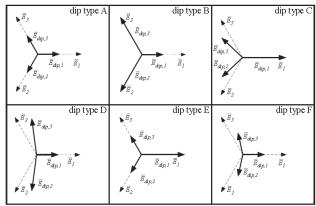

According to [8] depending on the type of fault (threephase, phase-to-phase with or without ground, single-phase to ground), the resulting voltage dip at the PCC can be one of six types displayed in Fig.2. Wind turbine is usually connected to the medium voltage grid through Dyn connected distribution transformer. This results in a transformation of the dip characteristic as listed in Table II. It can be concluded that voltage dips that affect the wind turbine converter on the secondary of the Dyn-transformer can only be of type A, C or D.

Fig. 2: Voltage dip classification "A" to "F". Phasors of three-phase voltage before (dotted) and during fault (solid) are shown. [8]

TABLE I

MAIN PARAMETERS OF FULL-CONVERTER TEST BENCHES

| Parameter                             | Down-scaled | Full-scaled |

|---------------------------------------|-------------|-------------|

| Line voltage U <sub>n</sub> [V]       | 400         | 690         |

| Power S <sub>n</sub> [kVA]            | 8.2         | 1800        |

| Filter inductance $L_1$ [mH]          | 1.7         | 0.05        |

| Filter capacitance $C_1$ [µF]         | 1           | 68          |

| Filter inductance L <sub>2</sub> [mH] | 4.1         | 0.09        |

| Filter capacitance $C_2$ [µF]         | 2.2         | 204         |

| Max DC-link voltage $U_{dc}$ [V]      | 750         | 1100        |

| Switching frequency fsw [kHz]         | 3.6         | 3.6         |

Investigating the phasors shown in Fig. 2, simple expressions of faulted phase voltages in LV level can be derived as a function of MV level fault factor k = 0...1. Transformation of three-phase dip voltages into a space-vector form the xy-components listed in Table II right

column are obtained. Examples of voltage dip generation using expressions of Table II are illustrated in Figs. 3-5.

TABLE II

VOLTAGE DIP CLASSIFICATION, PROPAGATION THROUGH DYN

CONNECTED TRANSFORMER AND SPACE-VECTOR GENERATION

| Fault              | Dip in MV<br>level | Dip in LV<br>level | Generation (LV)                                             |

|--------------------|--------------------|--------------------|-------------------------------------------------------------|

| 3-phase fault      | Туре А             | Туре А             | $u_{x,dip} = (1-k)u_{x,ref}$ $u_{y,dip} = (1-k)u_{y,ref}$   |

| 1-phase fault      | Туре В             | Type C             | $u_{x,dip} = u_{x,ref}$ $u_{y,dip} = (1-k)u_{y,ref}$        |

| phase-to-<br>phase | Type C             | Type D             | $u_{x,dip} = (1-k)u_{x,ref}$ $u_{y,dip} = u_{y,ref}$        |

| 2-phase to ground  | Type E             | Type F             | $u_{x,dip} = (1-k)u_{x,ref}$ $u_{y,dip} = (1-k/3)u_{y,ref}$ |

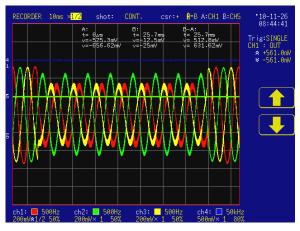

Fig. 3: Phase-to-phase voltages in dip of type B/C. Fault factor k = 0.5. Y-scale 200V/div, x-scale 20ms/div.

#### IV. EXPERIMENTAL RESULTS

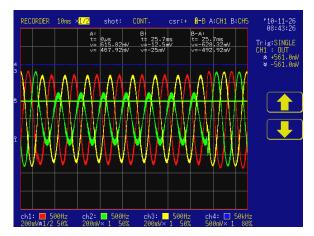

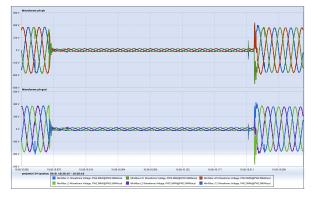

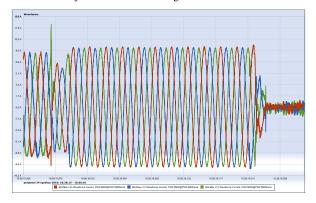

Figs. 6-9 illustrates the performance of the down-scaled test bench. All LVRT tests were conducted at 90% of the nominal active power of the EUT. Figs. 6-7 show a threephase symmetrical voltage fault down to zero. Due to dynamic grid voltage support of EUT grid side converter by injection of capacitive reactive current the observed output voltage is increased.

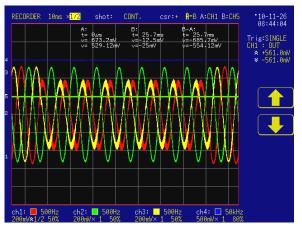

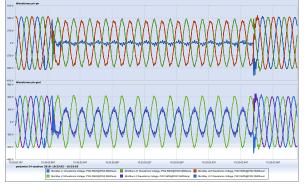

In Figs. 8-9 an unsymmetrical fault of type C when the fault factor k=1 are shown. Dynamic grid voltage support was disabled in this measurement.

Fig. 4: Phase-to-phase voltages in dip of type C/D. Fault factor k = 0.5. Y-scale 200V/div, x-scale 20ms/div.

Fig. 5: Phase-to-phase voltages in dip of type E/F. Fault factor k = 0.5. Y-scale 200V/div, x-scale 20ms/div.

Fig. 6: Grid emulator output voltages (phase-to-phase, upper, phase voltages, lower) during a 250 ms symmetrical voltage dip to 0%  $U_n$  with reactive current injection from the tested grid side converter.

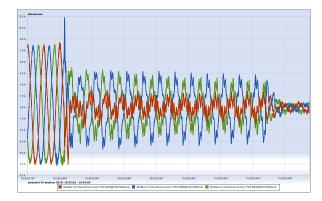

Fig. 7: Phase currents of the tested grid side converter during a 250 ms symmetrical voltage dip to 0%  $U_n$ . Dynamic grid voltage support by reactive current injection enabled.

Fig. 8: Grid emulator output voltages (phase-to-phase, upper, phase voltages, lower) during a 250 ms unsymmetrical type C voltage dip to 0%  $U_{\rm n}$ .

Fig. 9: Phase currents of the tested grid side converter during a 250 ms unsymmetrical type C voltage dip to  $0\% U_n$ . Dynamic grid voltage support by reactive current injection disabled.

## V. CONCLUSIONS

A full converter based test bench for low voltage ridethrough testing of wind turbine converters by means of voltage controlled grid emulator was presented. The structure of the test bench and the principles of voltage dip generation were explained. Measurement results illustrating excellent dynamic performance of the test bench were shown.

# REFERENCES

- M.Tsili, S. Papathanassiou, "A review of grid code technical requirements for wind farms", IET Renewable Power Generation, vol. 3, no. 3, pp. 3008-332, Sept. 2009.

- [2] C. Wessels, R. Lohde, F.W. Fuchs, "Transformer based voltage sag generator to perform LVRT and HVRT tests in the laboratory", EPE-PEMC 2010, Ohrid, Republic of Macedonia.

- [3] IEC 61400-21:2008, "Wind turbines Part 21: Measurement and assessment of power quality characteristics of grid connected wind turbines"

- [4] J. Niiranen, S. Seman, J.-P. Matsinen, R. Virtanen, A. Vilhunen, "Technical paper: Low voltage ride-through testing of wind turbine converters at ABB helps wind turbines meet the requirements of IEC 61400-21 more quickly", ABB 2009, [Online]. Avalailable: http://www.abb.com/cawp/seitp202/f47ea6b82b78a987852575a0004 4e446.aspx

- [5] R. Lohde, F.W. Fuchs, "Laboratory type PWM grid emulator for generating disturbed voltages for testing grid connected devices", EPE'09, Barcelona, Spain, 2009.

- [6] C. Saniter, J. Janning, "Test bench for grid code simulations for multi-MW wind turbines, design and control", IEEE Trans. Power Elec., vol. 23, no. 4, pp. 1707-1715, July 2008.

- [7] S. Hu, J. Li, H. Xu, "Comparison of voltage sag generators for wind power system", APPEEC 2009, Wuhan, China.

- [8] L. D. Zhang, M. H. J. Bollen, ""Characteristic of voltage dips (sags) in power systems," IEEE Trans. on Power Del., vol. 15, no. 2, pp. 827–832, April 2000.